~ cd 7. моделирование на уровне вентилей и переключателей в verilog hdl

В языке Verilog HDL предопределены 14 логических вентилей и 12 переключателей, что обеспечивает возможность моделирования на уровне вентилей и переключателей. Моделирование с помощью логических вентилей и переключателей имеет следующие преимущества:

- Вентили обеспечивают гораздо более тесное соответствие между реальной схемой и моделью.

- Не существует непрерывного назначения, эквивалентного двунаправленным передаточным вентилям.

Заметка Админа: В настоящем стандарте(IEEE STD 1364 -2005) описаны терминальные соединения(входные, выходные и двунаправленны). Под термином «Терминал» [Terminal] понимаются зажим, клемма на соединения на вентилях, примитивах, модулях и переключателях. Пример: «… терминальное входное соединение…» означает «входной зажим». В данном тексте используются две формы записи.

Перевод Официального Стандарта Verilog HDL

7.1 Синтаксис объявления вентилей и переключателей

Синтаксис 7-1 показывает синтаксис объявления вентилей и переключателей.

Декларация экземпляра вентиля и переключателя должна иметь следующие характеристики:

- Ключевое слово, называющее тип примитива вентиля или переключателя

- Дополнительная сила привода

- Необязательная задержка распространения

- Необязательный идентификатор, дающий имя каждому экземпляру вентиля или переключателя

- Необязательный диапазон для массива экземпляров

- Список терминальных соединений

Несколько экземпляров одного типа примитива вентиля или переключателя могут быть объявлены в виде списка, разделенного запятыми. Все такие экземпляры должны иметь одинаковые

gate_instantiation ::=

cmos_switchtype [delay3] cmos_switch_instance { , cmos_switch_instance } ;

| enable_gatetype [drive_strength] [delay3] enable_gate_instance { , enable_gate_instance } ;

| mos_switchtype [delay3] mos_switch_instance { , mos_switch_instance } ;

| n_input_gatetype [drive_strength] [delay2] n_input_gate_instance {, n_input_gate_instance };

| n_output_gatetype [drive_strength] [delay2] n_output_gate_instance { , n_output_gate_instance } ;

| pass_en_switchtype [delay2] pass_enable_switch_instance {, pass_enable_switch_instance } ;

| pass_switchtype pass_switch_instance { , pass_switch_instance } ;

| pulldown [pulldown_strength] pull_gate_instance { , pull_gate_instance } ;

| pullup [pullup_strength] pull_gate_instance { , pull_gate_instance } ;

cmos_switch_instance ::= [ name_of_gate_instance ] ( output_terminal , input_terminal , ncontrol_terminal , pcontrol_terminal )

enable_gate_instance ::= [ name_of_gate_instance ] ( output_terminal , input_terminal , enable_terminal )

mos_switch_instance ::= [ name_of_gate_instance ] ( output_terminal , input_terminal , enable_terminal )

n_input_gate_instance ::= [ name_of_gate_instance ] ( output_terminal , input_terminal { , input_terminal } )

n_output_gate_instance ::= [ name_of_gate_instance ] ( output_terminal { , output_terminal } , input_terminal )

pass_switch_instance ::= [ name_of_gate_instance ] ( inout_terminal , inout_terminal )

pass_enable_switch_instance ::= [ name_of_gate_instance ] ( inout_terminal , inout_terminal , enable_terminal )

pull_gate_instance ::= [ name_of_gate_instance ] ( output_terminal )

name_of_gate_instance ::= gate_instance_identifier [ range ]

pulldown_strength ::=

( strength0 , strength1 )

| ( strength1 , strength0 )

| ( strength0 )

pullup_strength ::=

( strength0 , strength1 )

| ( strength1 , strength0 )

| ( strength1 )

enable_terminal ::= expression

inout_terminal ::= net_lvalue

input_terminal ::= expression

ncontrol_terminal ::= expression

output_terminal ::= net_lvalue

pcontrol_terminal ::= expression

cmos_switchtype ::= cmos | rcmos

enable_gatetype ::= bufif0 | bufif1 | notif0 | notif1

mos_switchtype ::= nmos | pmos | rnmos | rpmos

n_input_gatetype ::= and | nand | or | nor | xor | xnor

n_output_gatetype ::= buf | not

pass_en_switchtype ::= tranif0 | tranif1 | rtranif1 | rtranif0

pass_switchtype ::= tran | rtran7.1.1 Спецификация типа вентилей

Объявление экземпляра вентиля или переключателя должно начинаться с ключевого слова, которое определяет примитив вентиля или переключателя, используемый экземплярами, которые следуют в объявлении. В таблице 7-1 перечислены ключевые слова, с которых должно начинаться объявление экземпляра вентиля или переключателя.

| n_input gates | n_output gates | Three-state gates | Pull gates | MOS switches | Bidirectional switches |

|---|---|---|---|---|---|

| and | buf | bufif0 | pulldown | cmos | rtran |

| nand | not | bufif1 | pullup | nmos | rtranif0 |

| nor | notif0 | pmos | rtranif1 | ||

| or | notif1 | rcmos | tran | ||

| xnor | rnmos | tranif0 | |||

| xor | rpmos | tranif1 |

Пояснения к встроенным вентилям и переключателям, показанным в таблице 7-1, приведены в разделе 7.2.

7.1.2 Спецификация силы источника

Необязательная спецификация силы источника должна определять силу логических значений на выходных клеммах экземпляра вентиля. Только экземпляры примитивов вентилей, показанных в таблице 7-2, могут иметь спецификацию силы источника.

| and | nand | buf | not | pulldown |

|---|---|---|---|---|

| or | nor | bufif0 | notif0 | pullup |

| xor | xnor | bufif1 | notif1 |

Спецификация силы сигнала для экземпляра вентиля, за исключением pullup и pulldown, должна иметь спецификацию strength1 и спецификацию strength0. Спецификация strength1 определяет силу сигналов с логическим значением 1, а спецификация strength0 — силу сигналов с логическим значением 0. Спецификация силы должна следовать за ключевым словом типа вентиля и предшествовать любой спецификации задержки. Спецификация strength0 может предшествовать или следовать за спецификацией strength1. Спецификации strength1 и strength0 должны быть разделены запятой и заключены в пару круглых скобок.

Вентиль pullup может иметь только спецификацию strength1; спецификация strength0 является необязательной. Вентиль pullldown может иметь только спецификацию strength0; спецификация strength1 является необязательной. Более подробно см. раздел 7.8.

Спецификация strength1 должна быть одним из следующих ключевых слов: supply1, strong1, pull1 или weak1.

Спецификация strength0 должна быть одним из следующих ключевых слов: supply0, strong0, pull0 и weak0.

Указание highz1 в качестве strength1 заставит вентиль или переключатель выдать логическое значение z вместо 1. Указание highz0 заставит вентиль выдать логическое значение z вместо 0. Спецификации силы (highz0, highz1) и (highz1, highz0) считаются ошибкой.

При отсутствии спецификации силы, экземпляры должны иметь силы по умолчанию strong1 и strong0.

Например:

В следующем примере показана спецификация силы источника в объявлении открытого коллектора nor вентиля:

nor (highz1,strong0) n1(out1,in1,in2);В этом примере nor выводит z вместо 1.

Более подробно моделирование логической силы рассматривается в разделах 7.9—7.13.

7.1.3 Спецификация задержки

Необязательная спецификация задержки должна определять задержку распространения через вентили и переключатели в объявлении. Вентили и переключатели в объявлениях без спецификации задержки не должны иметь задержки распространения. Спецификация задержки может содержать до трех значений задержки, в зависимости от типа вентиля. Объявления экземпляров pullup и pulldown не должны содержать спецификаций задержки. Более подробно задержки рассматриваются в разделе 7.14.

7.1.4 Идентификатор экземпляра примитива

Экземпляру вентиля или переключателя может быть присвоено необязательное имя. Если несколько экземпляров объявлены как массив экземпляров, для наименования экземпляров должен использоваться идентификатор.

7.1.5 Спецификация диапазона

Существует множество ситуаций, когда требуются повторяющиеся экземпляры. Эти экземпляры должны отличаться друг от друга только индексом вектора, с которым они связаны.

Чтобы указать массив экземпляров, за именем экземпляра следует спецификация диапазона. Диапазон должен быть задан двумя постоянными выражениями, левым индексом (lhi) и правым индексом (rhi), разделенными двоеточием и заключенными в пару квадратных скобок.

Спецификация диапазона [lhi:rhi] должна представлять массив экземпляров abs(lhi-rhi)+1. Ни одно из двух постоянных выражений не обязательно должно быть нулевым, и lhi не обязательно должно быть больше rhi. Если оба константных выражения равны, генерируется только один экземпляр.

Массив экземпляров должен иметь непрерывный диапазон. Один идентификатор экземпляра должен быть связан только с одним диапазоном для объявления массива экземпляров.

Спецификация диапазона должна быть необязательной. Если спецификация диапазона не задана, создается один экземпляр.

Например:

Декларация, представленная ниже, является неправильной:

nand #2 t_nand[0:3] ( ... ), t_nand[4:7] ( ... );Он может быть правильно объявлен как один массив из восьми экземпляров или как два массива с уникальными именами по четыре элемента в каждом:

nand #2 t_nand[0:7] ( ... );

nand #2 x_nand[0:3] ( ... ), y_nand[4:7] ( ... );7.1.6 Список соединений экземпляра примитивов

Список выводов описывает, как вентиль или переключатель соединяются с остальной частью модели. Тип вентиля или переключателя может ограничивать эти выражения. Список соединений должен быть заключен в пару круглых скобок, а клеммы должны быть разделены запятыми.

Выходные или двунаправленные клеммы всегда должны стоять первыми в списке клемм, за ними должны следовать входные клеммы.

Терминальные соединения для массива экземпляров должны соответствовать этим правилам:

- Длина бита каждого выражения порта в объявленном массиве экземпляров должна быть сравнена с длиной бита каждого отдельного экземпляра порта или терминала в экземпляре модуле или примитиве.

- Для каждого порта или клеммы, где длина бита выражения порта массива экземпляров такая же, как длина бита порта единичного экземпляра, выражение порта массива экземпляров должно быть подключено к каждому порту единичного экземпляра.

- Если длины битов различны, каждый экземпляр должен получить частичную выборку выражения порта, как указано в диапазоне, начиная с правого индекса.

- Слишком большое или слишком малое количество битов для подключения ко всем экземплярам считается ошибкой.

Ссылка на отдельный экземпляр из массива экземпляров осуществляется так же, как и ссылка на элемент массива регистров.

Например:

Пример 1 — Следующее объявление nand_array объявляет четыре экземпляра, на которые можно ссылаться через nand_array[1], nand_array[2], nand_array[3] и nand_array[4], соответственно.

nand #2 nand_array[1:4]( ... ) ;Пример 2 — Два следующих описания модуля эквивалентны, за исключением индексированных имен экземпляров, и они демонстрируют спецификацию диапазона и правила подключения для объявления массива экземпляров:

module driver (in, out, en);

input [3:0] in;

output [3:0] out;

input en;

bufif0 ar[3:0] (out, in, en); // массив буфферов третьего состояния

endmodule

module driver_equiv (in, out, en);

input [3:0] in;

output [3:0] out;

input en;

bufif0 ar3 (out[3], in[3], en); // каждый буфер объявляется отдельно

bufif0 ar2 (out[2], in[2], en);

bufif0 ar1 (out[1], in[1], en);

bufif0 ar0 (out[0], in[0], en);

endmoduleПример 3 — Два следующих описания модуля эквивалентны, за исключением индексированных имен экземпляров, и они демонстрируют, как различные экземпляры в массиве экземпляров соединяются, когда размеры портов не совпадают:

module busdriver (busin, bushigh, buslow, enh, enl);

input [15:0] busin;

output [7:0] bushigh, buslow;

input enh, enl;

driver busar3 (busin[15:12], bushigh[7:4], enh);

driver busar2 (busin[11:8], bushigh[3:0], enh);

driver busar1 (busin[7:4], buslow[7:4], enl);

driver busar0 (busin[3:0], buslow[3:0], enl);

endmodule

module busdriver_equiv (busin, bushigh, buslow, enh, enl);

input [15:0] busin;

output [7:0] bushigh, buslow;

input enh, enl;

driver busar[3:0] (.out({bushigh, buslow}), .in(busin),

.en({enh, enh, enl, enl}));

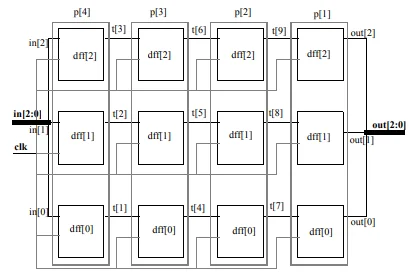

endmoduleПример 4 — Данный пример демонстрирует, как можно соединить ряд модулей в цепочку. На рисунке 7-1 показано эквивалентное схематическое соединение экземпляров DFF.

module dffn (q, d, clk);

parameter bits = 1;

input [bits-1:0] d;

output [bits-1:0] q;

input clk ;

DFF dff[bits-1:0] (q, d, clk); // объявление столбца D-триггеров

endmodule

module MxN_pipeline (in, out, clk);

parameter M = 3, N = 4; // M=ширина, N=глубина

input [M-1:0] in;

output [M-1:0] out;

input clk;

wire [M*(N-1):1] t;

// #(M) переопределяет параметр bits для dffn

// создаем столбцы p[1:N] из строк dffn (конвейер)

dffn #(M) p[1:N] ({out, t}, {t, in}, clk);

endmodule

7.2 Вентили and, nand, nor, or, or, xor, и xnor

Объявление экземпляра логического вентиля с несколькими входами должно начинаться с одного из следующих ключевых слов: and, nand, nor, or, xor или xnor.

Спецификация задержки должна быть нулевой, одной или двумя задержками. Если спецификация содержит две задержки, первая задержка определяет задержку нарастания выходного сигнала, вторая задержка определяет задержку спада выходного сигнала, и меньшая из двух задержек применяется к переходам выхода в x. Если указана только одна задержка, она должна определять как задержку нарастания, так и задержку спада. Если задержка не указана, то задержка распространения через вентиль должна отсутствовать.

Эти шесть логических вентилей должны иметь один выход и один или несколько входов. Первая клемма в списке клемм должна подключаться к выходу вентиля, а все остальные клеммы подключаются к его входам.

Таблицы истинности для этих вентилей, показывающие результат двух входных показаны в таблице 7-3.

| and | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | x | x |

| x | 0 | x | x | x |

| z | 0 | x | x | x |

| or | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 0 | 1 | x | x |

| 1 | 1 | 1 | 1 | 1 |

| x | x | 1 | x | x |

| z | x | 1 | x | x |

| xor | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 0 | 1 | x | x |

| 1 | 1 | 0 | x | x |

| x | x | x | x | x |

| z | x | x | x | x |

| nand | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | x | x |

| x | 1 | x | x | x |

| z | 1 | x | x | x |

| nor | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 1 | 0 | x | x |

| 1 | 0 | 0 | 0 | 0 |

| x | x | 0 | x | x |

| z | x | 0 | x | x |

| xnor | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 1 | 0 | x | x |

| 1 | 0 | 1 | x | x |

| x | x | x | x | x |

| z | x | x | x | x |

Версии этих шести логических вентилей, имеющие более двух входов, должны иметь естественное расширение, но количество входов не должно изменять задержки распространения.

Например:

В следующем примере объявлены вентиль с двумя входами:

and a1 (out, in1, in2);Входами являются in1 и in2. Выходом является out. Имя экземпляра — a1.

7.3 Вентили buf и not

Объявление экземпляра логического вентиля с несколькими выходами должно начинаться с одного из следующих ключевых слов: buf или not

Спецификация задержки должна быть нулевой, одной или двумя задержками. Если спецификация содержит две задержки, первая задержка определяет задержку нарастания выходного сигнала, вторая задержка определяет задержку спада выходного сигнала, и меньшая из двух задержек применяется к переходам выхода в x. Если указана только одна задержка, она должна определять как задержку нарастания, так и задержку спада. Если задержка не указана, то задержка распространения через вентиль должна отсутствовать.

Эти два логических вентиля должны иметь один вход и один или несколько выходов. Последняя клемма в списке клемм должна подключаться к входу логического вентиля, а остальные клеммы должны подключаться к выходам логического вентиля.

Таблицы истинности для этих логических вентилей с одним входом и одним выходом показаны в таблице 7-4.

| not input | not output |

|---|---|

| 0 | 0 |

| 1 | 1 |

| x | x |

| z | x |

| not input | not output |

|---|---|

| 0 | 1 |

| 1 | 0 |

| x | x |

| z | x |

Например:

Следующий пример объявляет двухвыводной buf:

buf b1 (out1, out2, in);Входом является in. Выходами являются out1 и out2. Имя экземпляра — b1.

7.4 Переключатели bufif1, bufif0, notif1 и notif0

Объявление экземпляра этих трехпозиционных логических вентилей должно начинаться с одного из следующих ключевых слов: bufif0, bufif1, notif1 или notif0.

Эти четыре логических вентиля моделируют трехпозиционные драйверы. Помимо логических значений 1 и 0, эти вентили могут выводить z.

Спецификация задержки должна быть нулевой, одной, двумя или тремя задержками. Если спецификация задержки содержит три задержки, то первая задержка определяет задержку нарастания, вторая — задержку спада, третья — задержку перехода в z, а наименьшая из трех задержек определяет задержку перехода в x. Если спецификация содержит две задержки, то первая задержка определяет задержку нарастания выходного сигнала, вторая — задержку спада выходного сигнала, а меньшая из двух задержек применяется к переходам выхода в x и z. Если указана только одна задержка, то она должна определять задержку для всех переходов выхода. Если задержка не указана, то задержка распространения через вентиль должна отсутствовать.

Некоторые комбинации входных значений данных и входных значений управления могут привести к тому, что эти вентили выдадут любое из двух значений, без предпочтения одного из них (см. 7.10.2). Логические таблицы для этих вентилей включают два символа, представляющие такие неизвестные результаты. Символ L должен представлять результат, имеющий значение 0 или z. Символ H должен представлять результат, имеющий значение 1 или z. Задержки при переходе к H или L рассматриваются так же, как и задержки при переходе к x.

Эти четыре логических вентиля должны иметь один выход, один вход данных и один вход управления. Первая клемма в списке клемм должна подключаться к выходу, вторая — к входу данных, а третья — к управляющему входу.

В таблице 7-5 представлены логические таблицы для этих вентилей.

| bufif0 | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 0 | z | L | L |

| 1 | 1 | z | H | H |

| x | x | z | x | x |

| z | x | z | x | x |

| bufif1 | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | z | 0 | L | L |

| 1 | z | 1 | H | H |

| x | z | x | x | x |

| z | z | x | x | x |

| notif0 | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 1 | z | H | H |

| 1 | 0 | z | L | L |

| x | x | z | x | x |

| z | x | z | x | x |

| notif1 | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | z | 1 | H | H |

| 1 | z | 0 | L | L |

| x | z | x | x | x |

| z | z | x | x | x |

Например:

Следующий пример объявляет экземпляр bufif1:

bufif1 bf1 (outw, inw, controlw);Выход — outw, вход — inw, управление — controlw. Имя экземпляра — bf1.

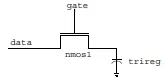

7.5 МОП-переключатели

Объявление экземпляра переключателя MOS должно начинаться с одного из следующих ключевых слов: cmos, nmos, pmos, rcmos, rnmos или rpmos.

Переключатели cmos и rcmos описаны в разделе 7.7.

Ключевое слово pmos обозначает транзистор P-типа металл-оксид-полупроводник (PMOS), а ключевое слово nmos — транзистор N-типа металл-оксид-полупроводник (NMOS). Транзисторы PMOS и NMOS имеют относительно низкий импеданс между истоком и стоком, когда они проводят ток. Ключевое слово rpmos означает резистивный PMOS-транзистор, а ключевое слово rnmos — резистивный NMOS-транзистор. Резистивные PMOS и резистивные NMOS транзисторы имеют значительно большее сопротивление между истоками и стоками при проводимости, чем PMOS и NMOS транзисторы. Нагрузочные устройства в статических сетях MOS являются примерами транзисторов rpmos и rnmos. Эти четыре переключателя представляют собой однонаправленные каналы для данных, аналогичные вентилям bufif.

Спецификация задержки должна быть нулевой, одной, двумя или тремя задержками. Если спецификация задержки содержит три задержки, то первая задержка определяет задержку нарастания, вторая — задержку спада, третья — задержку перехода в z, а наименьшая из трех задержек определяет задержку перехода в x. Если спецификация содержит две задержки, то первая задержка определяет задержку нарастания выходного сигнала, вторая — задержку спада, а меньшая из двух задержек применяется к переходам выхода в x и z. Если указана только одна задержка, то она должна определять задержку для всех переходов выхода. Если задержка не указана, то задержка распространения через переключатель должна отсутствовать.

Некоторые комбинации входных значений данных и входных значений управления могут заставить эти переключатели выдать любое из двух значений, без предпочтения одного из них. Логические таблицы для этих переключателей включают два символа, представляющие такие неизвестные результаты. Символ L представляет результат, имеющий значение 0 или z. Символ H представляет результат, имеющий значение 1 или z. Задержки при переходах к H и L должны быть такими же, как задержки при переходах к x.

Эти четыре переключателя должны иметь один выход, один вход данных и один вход управления. Первая клемма в списке клемм должна подключаться к выходу, вторая — к входу данных, а третья — к входу управления.

Переключатели nmos и pmos должны пропускать сигналы со своих входов и через свои выходы с изменением силы сигнала только в одном случае, как описано в п. 7.11. Переключатели rnmos и rpmos должны уменьшать силу сигналов, проходящих через них, как описано в п. 7.12.

В таблице 7-6 представлены логические таблицы для этих переключателей.

| pmos rpmos | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | 0 | z | L | L |

| 1 | 1 | z | H | H |

| x | x | z | x | x |

| z | z | z | z | z |

| nmos rnmos | 0 | 1 | x | z |

|---|---|---|---|---|

| 0 | z | 0 | L | L |

| 1 | z | 1 | H | H |

| x | z | x | x | x |

| z | z | z | z | z |

Например:

В следующем примере объявляется переключатель pmos:

pmos p1 (out, data, control);Выход — out, вход данных — data, вход управления — control. Имя экземпляра — p1.

7.6 Двунаправленные проходные переключатели

Объявление экземпляра двунаправленного проходного переключателя должно начинаться с одного из следующих ключевых слов: tran, tranif1, tranif0, rtran, rtranif1 или rtranif0.

Двунаправленные проходные переключатели не должны задерживать проходящие через них сигналы. Когда устройства tranif0, tranif1, rtranif0 или rtranif1 выключены, они должны блокировать сигналы, а когда они включены, они должны пропускать сигналы. Устройства tran и rtran не могут быть выключены, и они всегда должны пропускать сигналы.

Спецификация задержки для устройств tranif1, tranif0, rtranif1 и rtranif0 должна быть нулевой, одной или двумя задержками. Если спецификация содержит две задержки, то первая задержка определяет задержку включения, вторая — задержку выключения, и меньшая из двух задержек должна применяться к выходным переходам на x и z. Если указана только одна задержка, то она должна определять задержки включения и выключения. Если задержка не указана, задержка включения и выключения двунаправленного проходного переключателя должна отсутствовать.

Двунаправленные проходные переключатели tran и rtran не должны принимать спецификацию задержки.

Устройства tranif1, tranif0, rtranif1 и rtranif0 должны иметь три элемента в списках выводов. Первые два должны быть двунаправленными клеммами, которые проводят сигналы к устройствам и от них, а третья клемма должна подключаться к управляющему входу. Устройства tran и rtran должны иметь списки выводов, содержащие два двунаправленных вывода. Обе двунаправленные клеммы должны безусловно проводить сигналы к устройствам и от них, позволяя сигналам проходить через устройства в любом направлении. Двунаправленные клеммы всех шести устройств должны быть подключены только к скалярным сеткам или битовым выборкам векторных сеток.

Устройства tran, tranif0 и tranif1 должны пропускать сигналы с изменением их силы только в одном случае, как описано в п. 7.11. Устройства rtran, rtranif0 и rtranif1 должны уменьшать силу проходящих через них сигналов в соответствии с правилами, рассмотренными в п. 7.12.

Например:

Следующий пример объявляет экземпляр tranif1:

tranif1 t1 (inout1,inout2,control);Двунаправленные клеммы — inout1 и inout2. Управляющий вход — control. Имя экземпляра — t1.

7.7 КМОП-переключатели

Объявление экземпляра переключателя CMOS должно начинаться с одного из следующих ключевых слов: cmos или rcmos.

Спецификация задержки должна быть нулевой, одной, двумя или тремя задержками. Если спецификация задержки содержит три задержки, первая задержка определяет задержку нарастания, вторая — задержку спада, третья — задержку перехода на z, а наименьшая из трех задержек — задержку перехода на x. Задержки при переходе на H или L такие же, как и задержки при переходе на x.

Если спецификация содержит две задержки, то первая задержка определяет задержку нарастания выходного сигнала, вторая задержка определяет задержку спада выходного сигнала, а меньшая из двух задержек применяется к выходным переходам в x и z. Если указана только одна задержка, то она должна определять задержку для всех выходных переходов. Если задержка не указана, то задержка распространения через переключатель должна отсутствовать.

Переключатели cmos и rcmos должны иметь вход данных, выход данных и два входа управления. В списке выводов первый вывод подключается к выходу данных, второй — к входу данных, третий — к входу управления n-каналом, последний — к входу управления p-каналом.

Вентиль cmos должен пропускать сигналы с изменением их силы только в одном случае, как описано в п. 7.11. Вентиль rcmos должен уменьшать силу проходящих через него сигналов в соответствии с правилами, описанными в п. 7.12.

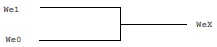

Переключатель cmos рассматривается как комбинация переключателя pmos и переключателя nmos. Переключатель rcmos должен рассматриваться как комбинация переключателя rpmos и переключателя rnmos. Комбинированные переключатели в этих конфигурациях должны иметь общие клеммы ввода и вывода данных, но должны иметь отдельные входы управления.

Например:

Эквивалентность cmos вентиля сопряжению nmos-вентиля и pmos-вентиля показана в следующем примере:

cmos (w, datain, ncontrol, pcontrol);эквивалентно:

nmos (w, datain, ncontrol);

pmos (w, datain, pcontrol);7.8 Источники pullup и puldown

Объявление экземпляра источника pullup или puldown должно начинаться с одного из следующих ключевых слов: pullup или puldown.

Источник pullup должен присвоить логическое значение 1 сетям, подключенным в его списке выводов. Источник pullldown должен присвоить логическое значение 0 сетям, подключенным в его списке выводов.

Сигналы, которые эти источники подают на сети, должны иметь силу pullup в отсутствие спецификации силы. Если для источника pullup задана strength1 или для источника pulldown задана strength0, сигналы должны иметь указанную силу. Спецификация strength0 на источнике pullup и спецификация strength1 на источнике оттягивания игнорируются.

Для этих источников не должно быть спецификаций задержки. Например:

В следующем примере объявлены два экземпляра pullup:

pullup (strong1) p1 (neta), p2 (netb);7.9 Моделирование логической силы

Язык Verilog HDL обеспечивает точное моделирование конкуренции сигналов, двунаправленных проходных вентилей, резистивных МОП-устройств, динамических МОП, разделения заряда и других конфигураций сети, зависящих от технологии, позволяя скалярным значениям чистого сигнала иметь полный диапазон неизвестных значений и различные уровни силы или сочетаний уровней силы. Такое многоуровневое моделирование логической силы разрешает комбинации сигналов в определенные или неопределенные значения, чтобы представить поведение аппаратуры с повышенной точностью.

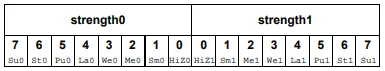

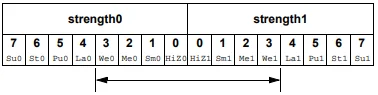

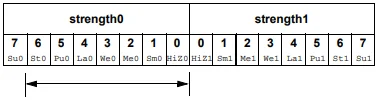

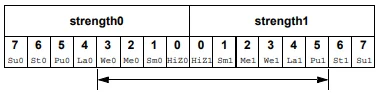

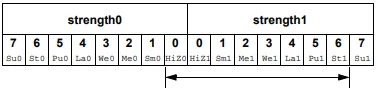

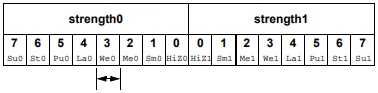

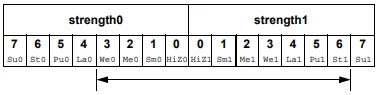

Спецификация силы должна состоять из двух компонентов:

1) Сила 0 части сети значения, называемая strength0, обозначается как одно из следующих значений: supply0, strong0, pull0, weak0 или highz0.

2) Сила 1 части сети значения, называемая strength1, обозначается как одно из следующих значений: supply1, strong1, pull1, weak1 или highz1.

Комбинации (highz0, highz1) и (highz1, highz0) считаются недопустимыми.

Несмотря на такое разделение спецификации силы, для прогнозирования результатов комбинаций сигналов полезно рассматривать силу как свойство, занимающее области континуума.

Таблица 7-7 демонстрирует континуум сильных сторон. В левой колонке перечислены ключевые слова, используемые при определении сильных сторон. В правой колонке приведены коррелирующие уровни силы.

| Strength name | Strength level |

|---|---|

| supply0 | 7 |

| strong0 | 6 |

| pull0 | 5 |

| large0 | 4 |

| weak0 | 3 |

| medium0 | 2 |

| small0 | 1 |

| highz0 | 0 |

| highz1 | 0 |

| small1 | 1 |

| medium1 | 2 |

| weak1 | 3 |

| large1 | 4 |

| pull1 | 5 |

| strong1 | 6 |

| supply1 | 7 |

В таблице 7-7 представлены четыре движущие силы: supply, strong, pull или weak.

Сигналы с силой заряда должны распространяться от выходов вентилей и выходов непрерывного назначения. В таблице 7-7 приведены три силы хранения заряда: large, medium или small.

Сигналы с накопительной силой заряда должны подаваться в сети типа trireg.

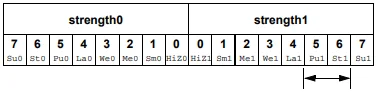

Силы сигналов в таблице 7-7 можно рассматривать как места на шкале на рисунка 7-8.

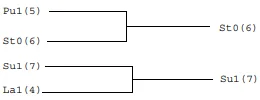

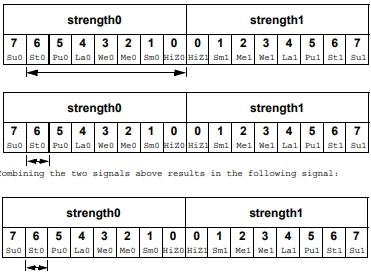

При обсуждении комбинаций сигналов далее в этом пункте используются графики, аналогичные тем, что приведены на рисунке 7-2.

Если значение сигнала сети известно, все уровни ее силы должны находиться либо в части strength0 шкалы, представленной на рисунке 7-2, либо все уровни силы должны находиться в части strength1. Если значение сигнала сети неизвестно, она должна иметь уровни силы как в части strength0, так и в части strength1. Сеть со значением сигнала z должна иметь уровень силы только в одном из делений 0 частей шкалы.

7.10 Силы и значения сочетающихся сигналов

В дополнение к значению сигнала сеть должна иметь либо один определенный уровень силы, либо неопределенную силу, состоящую из более чем одного уровня. Когда сигналы объединяются, их силы и значения должны определять силу и значение результирующего сигнала в соответствии с принципами, изложенными в 7.10.1-7.10.4.

7.10.1 Сочетание сигналов определенной силы

В этом подпункте рассматриваются сочетания сигналов, в которых каждый сигнал имеет определенное значение и один уровень силы.

Если два или более сигналов неравной силы объединяются в конфигурации проводной сети, более сильный сигнал доминирует над всеми более слабыми и определяет результат. Сочетание двух или более сигналов одинаковой силы должно приводить к одному и тому же значению с большей из всех сил. Сочетание сигналов, одинаковых по силе и значению, приводит к одному и тому же сигналу. Сочетание сигналов с разными значениями и одинаковой силой может иметь три возможных результата. Два из этих результатов возникают при наличии проводной логики, а третий — при ее отсутствии. Проводная логика обсуждается в разделе 7.10.4. Результат при отсутствии проводной логики рассматривается на рисунке 7-3 (в разделе 7.10.2).

Например:

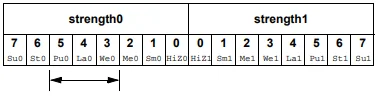

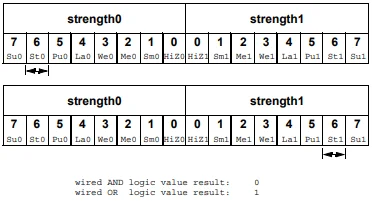

На рисунке 7-2 цифры в скобках указывают на относительную силу сигналов. Комбинация pull1 и strong0 приводит к появлению strong0, который является более сильным из двух сигналов.

7.10.2 Неопределенные силы: источники и сочетаний

Существует несколько классификаций сигналов, обладающих неопределенной силой:

- Сигналы с известными значениями и несколькими уровнями силы

- Сигналы со значением x, которые имеют уровни силы, состоящие из подразделений strength1 и strength0 части шкалы сил на рисунке 7-2

- Сигналы со значением L, которые имеют уровни силы, состоящие из высокого импеданса, соединенного с уровнями силы в части strength0 шкалы сил на рисунке 7-2

- Сигналы со значением H, которые имеют уровни силы, состоящие из высокого импеданса, объединенного с уровнями силы в части strength1 шкалы сил на рисунке 7-2

Многие конфигурации могут создавать сигналы неопределенной силы. Когда два сигнала равной силы и противоположного значения объединяются, результатом будет значение x, а также уровни силы обоих сигналов и все меньшие уровни силы.

Например:

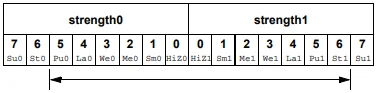

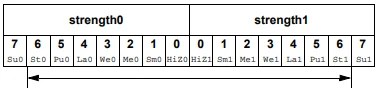

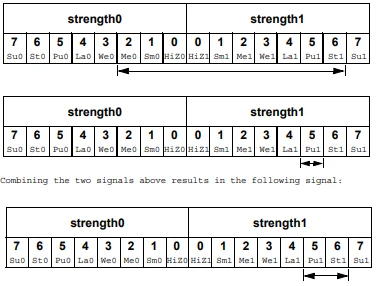

На рисунке 7-4 оказана сочетание weak сигнала со значением 1 и weak сигнала со значением 0, в результате чего получается сигнал со силой weak и значением x.

Этот выходной сигнал описан на рисунке 7-5.

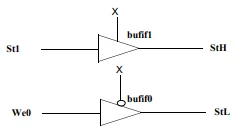

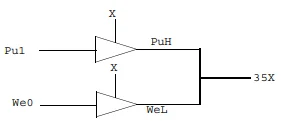

Неопределенный уровень сигнала может иметь диапазон возможных значений. Примером может служить уровень сигнала на выходе трехпозиционных драйверов с неизвестными управляющими входами, как показано на рисунке 7-6.

Выходом bufif1 на рисунке 7-6 является strong H, состоящая из диапазона значений, описанных на рисунке 7-7.

Выходом bufif0 на рисунке 7-6 является strong буква L, состоящая из диапазона значений, описанных на рисунке 7-8.

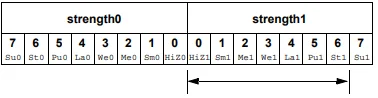

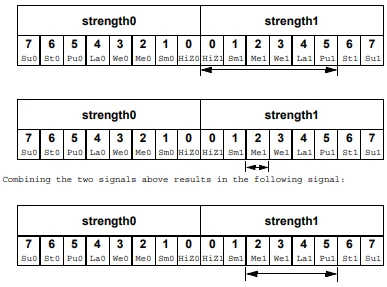

Сочетание двух сигналов с неопределенной силой должна приводить к сигналу с неопределенной силой. Результирующий сигнал должен иметь диапазон уровней силы, включающий уровни силы составляющих его сигналов. Примером может служить сочетание выходов двух трехпозиционных источников с неизвестными управляющими входами, показанная на рисунке 7-9.

На рисунке 7-9 сочетание сигналов неопределенной силы дает диапазон, включающий крайние значения сигналов и все значения между ними, как описано на рисунке 7-10.

Результатом является значение x, поскольку его диапазон включает значения 1 и 0. Число 35, которое предшествует x, представляет собой конкатенацию двух цифр. Первая — это цифра 3, которая соответствует наивысшему уровню strength0 для результата. Вторая цифра, 5, соответствует наивысшему уровню strength1 для результата.

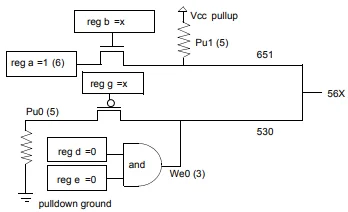

Сети коммутаторов(переключателей) могут создавать диапазоны напряжений одного и того же значения, как, например, сигналы от верхней и нижней конфигураций на рисунке 7-11.

На рисунке 7-11 верхняя сочетания из регистра, транзистора, управляемого регистра неопределенного значения, и подтягивающего устройства формирует сигнал со значением 1 и диапазоном напряжений (651), описанный на рисунке 7-12.

На рисунке 7-11 нижняя сочетание из pulldown, транзистора, управляемого регистром с неопределенным значением, и and вентиля вырабатывает сигнал со значением 0 и диапазоном напряжений (530), описанным на рисунке 7-13.

Когда сигналы от верхней и нижней конфигураций на рисунке 7-11 объединяются, в результате получается неизвестное с диапазоном (56x), определяемым крайними значениями двух сигналов, показанных на рисунке 7-14.

На рисунке 7-11 замена pulldown в нижней конфигурации на supply0 изменит диапазон результата на диапазон (StX), описанный на рисунке 7-15.

Диапазон на рисунке 7-15 является strong x, потому что он неизвестен, а экстремумы обеих его компонент strong. Экстремум выхода нижней конфигурации strong, потому что более низкий pmos уменьшает силу сигнала supply0. Эта особенность моделирования рассматривается в разделе 7.11.

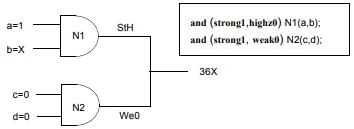

Логические вентили дают результаты с неоднозначными значениями силы, а также драйверы с тремя состояниями. Такой случай показан на рисунке 7-16. вентиль N1 объявлены с силой highz0, а N2 — с силой weak0.

На рисунке 7-16 reg b имеет неопределенное значение, поэтому на вход верхнего and затвора подается strong x. Верхний вентиль and имеет спецификацию силы, включающую highz0. Сигнал с верхнего строба and — это strong H, состоящий из значений, как описано на рисунке 7-17.

HiZ0 является частью результата, потому что в спецификации на силу для данного затвора указана эта сила для выхода со значением 0. Спецификация силы, отличная от высокого импеданса, для выхода со значением 0 приводит к значению выхода вентиля x. Выходом нижнего вентиля является weak 0, как описано на рисунке 7-18.

Когда сигналы сочетаются, получается диапазон (36x), как показано на рисунке 7-19.

На рисунке 7-19 представлена сочетание неопределенного и определенного сигналов. Такие комбинации являются темой раздела 7.10.3.

7.10.3 Неопределенные сигналы и определенный сигналы

Сочетание сигнала с определенной силой и известным значением с другим сигналом с неопределенной силой имеет несколько возможных случаев. Чтобы понять набор правил, регулирующих этот тип сочетаний, необходимо рассмотреть уровни силы сигнала неопределенной силы отдельно друг от друга и относительно сигнала определенной силы. Когда сигнал известной величины и определенной силы сочетается с компонентом сигнала неопределенной силы, правила должны быть такими:

1) Уровни силы неопределенного сигнала, которые превышают уровень силы определенного сигнала, остаются в результате.

2) Уровни силы неопределенного сигнала, которые меньше или равны уровню силы определенного сигнала, должны исчезнуть из результата, с учетом правила 3.

3) Если в результате выполнения правил 1 и 2 возникает разрыв в уровнях силы, поскольку сигналы имеют противоположное значение, сигналы в разрыве должны быть частью результата.

На следующих рисунках показаны некоторые варианты применения этих правил.

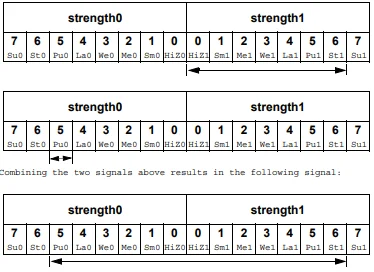

На рисунке 7-20 уровни силы неопределенного сигнала, которые меньше или равны уровню силы определенного сигнала, исчезают из результата, демонстрируя правило 2.

На рисунке 7-21 применяются правило 1, правило 2 и правило 3. Уровни силы неопределенного сигнала силы, которые имеют противоположное значение и меньшую силу, чем определенный сигнал силы, исчезают из результата. Уровни силы неопределенного сигнала силы, которые меньше, чем уровень силы определенного сигнала силы, и имеют одинаковое значение, исчезают из результата. Уровень силы определенного сигнала силы и больший экстремум неопределенного сигнала силы определяют диапазон в результате.

На рисунке 7-22 применяются правила 1 и 2. Уровни силы в неопределенном сигнале силы, которые меньше уровня силы определенного сигнала силы, исчезают из результата. Уровень силы определенного сигнала силы и уровень силы в большей крайней точке неопределенного сигнала силы определяют диапазон в результате.

На рисунке 7-23 действуют правила 1, 2 и 3. Большая крайняя точка диапазона значений силы для неопределенного сигнала силы больше, чем уровень силы определенного сигнала силы. В результате получается диапазон, определяемый наибольшей силой в диапазоне неопределенного сигнала силы и уровнем силы определенного сигнала силы.

7.10.4 Типы проводных логических сетей

Типы сетей triand, wand, trior и wor должны разрешать конфликты, когда несколько драйверов имеют одинаковую силу. Эти типы сетей должны исправлять значения сигналов, рассматривая их как входы логических функций.

Например:

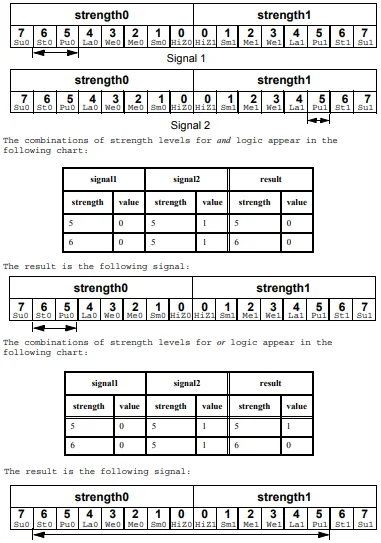

Рассмотрим сочетание двух сигналов определенной силы на рисунке 7-24.

Сочетание сигналов на рисунке 7-24 с использованием wired and логической схем дает результат с тем же значением, что и результат, полученный вентелем and, на входы которого поданы значения этих двух сигналов. Сочетание сигналов с использованием wired or логической схемы дает результат, равный результату, полученному с помощью вентиля or со значениями этих двух сигналов в качестве его входов. Сила результата в обоих случаях равна силе объединенных сигналов. Если значение верхнего сигнала изменится так, что оба сигнала на рисунке 7-24 будут иметь значение 1, то результаты обоих типов логики будут иметь значение 1.

Когда неопределенные силы сигналы объединяются в проводной логике, необходимо рассмотреть результаты всех сочетаний каждого из уровней силы в первом сигнале с каждым из уровней силы во втором сигнале, как показано на рисунке 7-25.

7.11 Снижение силы с помощью нерезистивных устройств

Переключатели nmos, pmos и cmos должны передавать напряжение со входа данных на выход, за исключением того, что сила supply должна быть снижена до strong силы.

Переключатели tran, tranif0 и tranif1 не должны влиять на уровень сигнала через двунаправленные клеммы, за исключением того, что уровень supply должен быть снижен до strong.

7.12 Снижение прочности с помощью резистивных устройств

Устройства rnmos, rpmos, rcmos, rtran, rtranif1 и rtranif0 должны уменьшать силу проходящих через них сигналов в соответствии с таблицей 7-8.

| Входная сила | Снижение прочности |

|---|---|

| Supply drive | Pull drive |

| Strong drive | Pull drive |

| Pull drive | Weak drive |

| Large capacitor | Medium capacitor |

| Weak drive | Medium capacitor |

| Medium capacitor | Small capacitor |

| Small capacitor | Small capacitor |

| High impedance | High impedance |

7.13 Сильные стороны типов сетей

Сети типов tri0, tri1, supply0 и supply1 должны генерировать сигналы с определенными уровнями силы. trireg в объявлении можно указать один из двух уровней силы сигнала, кроме уровня по умолчанию.

7.13.1 Силы сетей tri0 и tri1

Тип сети tri0 моделирует сеть, подключенную к резистивному устройству pulldown. В отсутствие переопределяющего источника такой сигнал должен иметь значение 0 и силу pullup. Тип сети tri1 моделирует сеть, подключенную к резистивному устройству pullup. В отсутствие переопределяющего источника такой сигнал должен иметь значение 1 и силу подтягивания.

7.13.2 Сила trireg

Тип trireg сеть моделирует узлы хранения заряда. Сила накопителя, полученного от сети trireg, находящейся в состоянии хранения заряда (то есть драйвер зарядил сеть, а затем перешел в высокоимпедансный режим), должна быть одной из этих трех сил: large, medium или small. Конкретная сила, связанная с конкретной сеткой trireg, должна быть указана пользователем в объявлении сети. По умолчанию используется сила medium. Синтаксис этой спецификации описан в разделе 4.4.1.

7.13.3 Силы сетей supply0 и supply1

Тип сети supply0 определяет соединения с землей. Тип сети supply1 моделирует соединения с источниками питания. Сетевые типы supply0 и supply1 должны иметь управляющие воздействия на источник силы supply.

7.14 Задержки на вентиле и в сети

Задержки в вентилях и сетках позволяют более точно описать задержки в цепи. Задержки вентиля определяют задержку распространения сигнала от любого входа вентиля до его выхода. Для каждого выхода можно задать до трех значений, представляющих задержки нарастания, спада и выключения (см. 7.2—7.8).

Задержки в сети означают время, которое проходит от момента изменения значения любого источника в сети до момента обновления и дальнейшего распространения значения в сети. Для каждой сети можно указать до трех значений задержки.

Для вентилей и сеток задержка по умолчанию равна нулю, если не задана спецификация задержки. Если задано одно значение задержки, то это значение должно использоваться для всех задержек распространения, связанных со стробом или сеткой. Если заданы две задержки, то первая задержка должна определять задержку нарастания, а вторая — задержку спада. Задержка при переходе сигнала в высокоимпедансное состояние или неизвестное должна быть меньшей из двух значений задержки.

Для спецификации с тремя задержками,

- Первая задержка относится к переходу к значению 1 (задержка нарастания).

- Вторая задержка относится к переходу к значению 0 (задержка падения).

- Третья задержка относится к переходу к высокоимпедансному значению.

Когда значение изменяется на неизвестное (x), задержка становится наименьшей из трех задержек. Сила входного сигнала не влияет на задержку распространения от входа к выходу.

В таблице 7-9 приведена информация о выборе задержки распространения от до для спецификаций с двумя и тремя задержками.

| От значения: | К значению: | Задержка используется, если есть | |

|---|---|---|---|

| 2 задержки | 3 задержки | ||

| 0 | 1 | d1 | d1 |

| 0 | x | min(d1, d2) | min(d1, d2, d3) |

| 0 | z | min(d1, d2) | d3 |

| 1 | 0 | d2 | d2 |

| 1 | x | min(d1, d2) | min(d1, d2, d3) |

| 1 | z | min(d1, d2) | d3 |

| x | 0 | d2 | d2 |

| x | 1 | d1 | d1 |

| x | z | min(d1, d2) | d3 |

| z | 0 | d2 | d2 |

| z | 1 | d1 | d1 |

| z | x | min(d1, d2) | min(d1, d2, d3) |

Например:

Пример 1 — Ниже приведен пример спецификации задержки с одной, двумя и тремя задержками:

and #(10) a1 (out, in1, in2); // только одна задержка

and #(10,12) a2 (out, in1, in2); // задержки нарастания и спада

bufif0 #(10,12,11) b3 (out, in, ctrl);// задержки нарастания, спада и выключенияПример 2 — В следующем примере задан простой модуль-защелка с тремя состояниями выходов, где для вентилей заданы индивидуальные задержки. Задержка распространения сигнала от первичных входов до выходов модуля будет суммарной и зависит от пути сигнала по сети.

module tri_latch (qout, nqout, clock, data, enable);

output qout, nqout;

input clock, data, enable;

tri qout, nqout;

not #5 n1 (ndata, data);

nand #(3,5) n2 (wa, data, clock),

n3 (wb, ndata, clock);

nand #(12,15) n4 (q, nq, wa),

n5 (nq, q, wb);

bufif1 #(3,7,13) q_drive (qout, q, enable),

nq_drive (nqout, nq, enable);

endmodule7.14.1 min:type:max задержки

Синтаксис задержек для примитивов вентилей (включая UDP; см. пункт 8), сетей и непрерывных назначений должен допускать по три значения для задержек нарастания, спада и выключения.

Минимальное, типичное и максимальное значения для каждой задержки должны быть указаны в виде выражений, разделенных двоеточиями. Между выражениями для минимальной, типичной и максимальной задержек не должно быть обязательной связи (например, min ≤ typ ≤ max). Это могут быть любые три выражения.

Например:

В следующем примере показаны значения min:typ:max для задержек нарастания, спада и выключения:

module iobuf (io1, io2, dir);

. . .

bufif0 #(5:7:9, 8:10:12, 15:18:21) b1 (io1, io2, dir);

bufif1 #(6:8:10, 5:7:9, 13:17:19) b2 (io2, io1, dir);

. . .

endmoduleparameter min_hi = 97, typ_hi = 100, max_hi = 107;

reg clk;

always begin

#(95:100:105) clk = 1;

#(min_hi:typ_hi:max_hi) clk = 0;

end7.14.2 Сети trireg потеря заряда

Как и все сети, спецификация задержки в объявлении сети trireg может содержать до трех задержек. Первые две задержки должны определять задержку перехода в логические состояния 1 и 0, когда сеть trireg переводится в эти состояния источником. Третья задержка должна определять время потери(распада) заряда вместо задержки перехода в логическое состояние z. Время потери заряда определяет задержку между выключением источником trireg-сетки и моментом, когда ее накопленный заряд больше не может быть определен.

Для trireg сети не требуется спецификация задержки выключения, поскольку trireg сеть никогда не осуществляет переход в логическое состояние z. Когда драйверы trireg сети переходят из логических состояний 1, 0 или x в выключенное состояние, trireg сеть должна сохранять предыдущее логическое состояние 1, 0 или x, в котором находились ее источник. Значение z не должно передаваться от источника trireg-сетки к trireg-сетке. Сеть trireg может удерживать логическое состояние z только в том случае, если z является начальным логическим состоянием сети trireg, или если сеть trireg принудительно переведена в состояние z с помощью оператора force (см. 9.3.2).

Спецификация задержки потери заряда моделирует неидеальный узел хранения заряда. То есть узел хранения заряда, заряд которого утекает через окружающие его устройства и соединения.

Процесс потери заряда и спецификация задержки для потери заряда описаны в 7.14.2.1 и 7.14.2.2, соответственно.

7.14.2.1 Процесс потери(распада) заряда

Потеря заряда — это причина перехода 1 или 0, хранящегося в trireg-сети, в неизвестное значение (x) после определенной задержки. Процесс потери заряда начинается, когда источники trireg-сетки выключаются и trireg-сетка начинает накапливать заряд. Процесс потери заряда должен завершиться при следующих двух условиях:

1) Задержка, заданная временем потери заряда, истекает, и trireg-сеть совершает переход из 1 в 0 до х.

2) Драйверы сети trireg включаются и передают 1, 0 или x в сеть trireg.

7.14.2.2 Спецификация задержки для времени потери заряда

Третья задержка в объявлении trireg-сети должна определять время потери заряда. Трехзначная спецификация задержки в объявлении trireg-сети должна иметь следующий вид:

#(d1, d2, d3) // (задержка нарастания, задержка спада, время затухания заряда)Спецификация времени потери заряда в декларации trireg-сети должна предшествовать спецификации задержки нарастания и спада.

Например:

Пример 1 — В следующем примере показана спецификация времени потери заряда в декларации

trireg (large) #(0,0,50) cap1;В этом примере объявлена сеть trireg с именем cap1. Эта trireg-сеть хранит большой заряд. Спецификации задержки нарастания равны 0, задержки спада равны 0, а спецификация времени спада заряда равна 50 единицам времени.

Пример 2 — В следующем примере представлен файл описания источника, содержащий объявление сети trireg со спецификацией времени потери заряда. На рисунке 7-26 показана эквивалентная схема для исходного описания.

module capacitor;

reg data, gate;

// trireg declaration with a charge decay time of 50 time units

trireg (large) #(0,0,50) cap1;

nmos nmos1 (cap1, data, gate); // nmos that drives the trireg

initial begin

$monitor("%0d data=%v gate=%v cap1=%v", $time, data, gate, cap1);

data = 1;

// Toggle the driver of the control input to the nmos switch

gate = 1;

#10 gate = 0;

#30 gate = 1;

#10 gate = 0;

#100 $finish;

end

endmodule